New overview paper on Argus to appear in IEEE Micro Special Issue

A new overview paper on Argus, our framework and generator for accelerating CNNs on FPGAs, has been accepted to appear in IEEE Micro, in a special issue on Machine Learning Acceleration.

This paper, “Argus: an End-to-End Framework for Accelerating CNNs on FPGAs,” was co-authored with PhD students Yongming Shen and Tianchu Ji and my collaborator Prof. Mike Ferdman.

Abstract: Advances in deep learning have led to the widespread use of convolutional neural networks (CNNs) for solving the most challenging computer vision problems. However, the high computational intensity of CNNs is beyond the capability of general-purpose CPUs, requiring specialized hardware acceleration. In particular, FPGAs have been shown effective for CNNs. Unfortunately, the difficulty of manually implementing CNN accelerators for FPGAs limits their adoption.

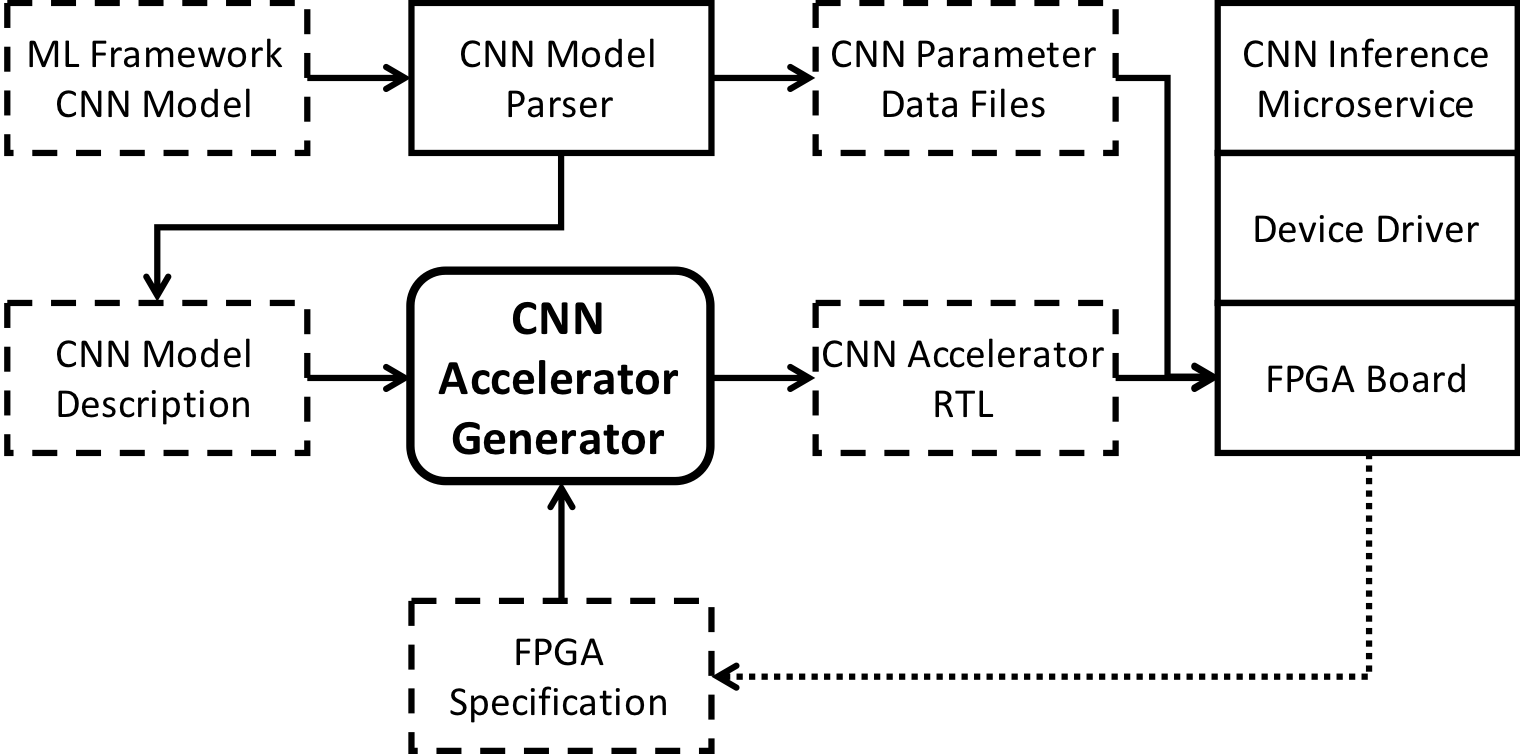

We present Argus, an end-to-end framework for accelerating CNNs on FPGAs. The core of Argus is an accelerator generator that translates high-level CNN descriptions into efficient multi-core accelerator designs. Argus explores an extensive design space, jointly optimizing all aspects of the design for the target FPGA and generating multi-core accelerator designs that achieve near-perfect dynamic arithmetic unit utilization. To minimize user effort, Argus includes a model parser for importing CNN models from popular machine learning frameworks, and a software stack for running an FPGA-backed CNN inference microservice.

This entry was posted on July 12, 2019.